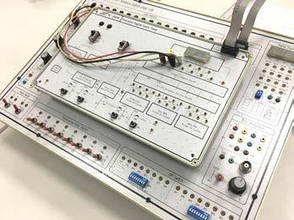

Стенд лабораторний "Цифровий логічній тренажер" KL-310

Цифровий логічних тренажер KL-310 призначена для студентів та інженерів, які розробляють та тестують прототипи схем. Вона містить схеми комбінаторної логіки, послідовної логіки, пам'яті, АЦП/ЦАП та інші експериментальні схеми. Є кілька схем програм (ШІМ, таймер, керування двигуном та ін.).

Все необхідне обладнання для експериментів із цифровою логікою — джерело живлення, синхронератор, перемикачі, дисплеї — є в головному блоці.

Лабораторія складається з 10 експериментальних модулів та однієї мікросхеми CPLD і модуля експериментальної макетної плати.

Особливості стенда KL-310:

- Тренажер повністю побудований на логічних схемах FPGA/CPLD. Кожен модуль має захисний буферний ланцюг і живиться від головного блока через силовий роз'єм, що запобігає неправильному подаванню живлення під час проведення досвіду.

- Дає змогу виконувати досліди з логічними схемами на різних рівнях, від комбінаторної та послідовної логіки до сполучення логічних схем із мікроконтролером і побутових практичних застосунків.

- Студенти можуть застосовувати свої схеми, зібрані за допомогою універсального пристрою CPLD і експериментального модуля макетної плати, що дає змогу збирати прототипи більшості аналогових і цифрових схем системи.

- Містить схеми АЦП і ЦАП різних типів для вивчення різних схем сполучення аналогових і цифрових сигналів.

- Вбудований 8-канальний мультиплексор у головному блоці для вимірювання різних цифрових сигналів у реальному часі.

- Різні режими роботи 4-розрядного 7-сегментного дисплея

(а) режим розгортки

(b) режим відбиття окремого розряду

(з) режим лічильника частоти для вимірювання внутрішньої та зовнішньої синхронізації.

- Вбудований 8-канальний мультиплексор у головному блоці для вимірювання різних цифрових сигналів у реальному часі.

- Різні режими роботи 4-розрядного 7-сегментного дисплея

(а) режим розгортки

(b) режим відбиття окремого розряду

(з) режим лічильника частоти для вимірювання внутрішньої та зовнішньої синхронізації.

-

Окремий ящик для кожного модуля, що забезпечує зручність зберігання й перенесення.

Перелік лабораторних робіт:

1. KL-34001 Експеримент із комбінаційною логічне схемою

(1) Схема НЕ-ІЛІ

(2) Схема НЕ-І

(3) Схема Виключає АБО

a. Побудова схеми Виключає АБО на елементах НЕ-І

b. Комбінації базових елементів

(4) І-ІЛІ-Інвертор (A-0-l)

(5) Схема компактора

a. Компактор, побудований на базових логічних елементах

b. Компактор, побудований на мікросхемах ТТЛ

(6) Схема Шміта

(7) Логічна схема з відкритим колектором

a. Схема високої напруги/струм

b. Побудова схеми І на затворі з відкритим колектором

(8) Схеми напівсумматора та повного суматора

Побудова напівсумматора на базових логічних елементів

(9) Схеми напіввичитувача та повного відчитувача Побудова віднімача на

базових логічних елементів

(10) Схема генератора контролю парності

Генератор контролю парності на елементах Виключає АБО

(11) Побудова декодера 4-10 на мікросхемах ТТЛ

(12) Перемикачні характеристики схеми перетворення рівня ТТЛ

2. KL-34002 Експеримент з арифметичною логікою, логікою з трьома

станами та перетворювачем коду

(1) Логічна схема з трьома станами КМОН на польовому транзисорі

a. Вимірювання таблиці істинності

b. Побудова схеми І на затворі з трьома станами

c. Ланцюг двоспрямованого передавання

(2) Схеми напівсумматора та повного суматора

a. Схема повного суматора на мікросхемі

b. Схема генератора з високошвидкісним сумером

c. Схема суматора двоїчно-десятичного коду

(3) Схеми напіввичитувача та повного відчитувача

Схеми повного суматора та інвертора

(4) Схема арифметико-логічного пристрою (АЛУ)

(5) Схема генератора перевірки парності

Мікросхема генератора перевірки парності

(6) Цифрове перетворення 16-ричного коду на десятичний/88ічний у 16-

гарячий

a. Перетворення восьмизначного десяткового коду на 16-чний

b. Перетворення восьмизначного 16-ричного коду в десятичний

3. KL-34003 Експеримент з логічними схемами кодера, декодера та

мультиплексера

(1) Схема кодера

a. Побудова кодера 4-2 на базових затворах

b. Побудова декодера 9-4 на мікросхемах ТТЛ

(2) Схема декодера

a. Побудова декодера 2-4 на базових затворах

b. Декодер двоїчно-десятичного коду в 7-сегментний код

(KL-34003 блок d)

(3) Схема мультиплексора

a. Побудова мультиплексора 2-в-1

b. Використання мультиплексорів для створення функцій

c. Побудова схеми мультиплексора на мікросхемах ТТЛ

(4) Схема демультиплексера

Побудова демультиплексера з 2 виходами на базових логічних елементах

(5) Схема аналогового мультиплексора/демультиплексера з цифровим контролем

(6) Перемикачні характеристики схеми перетворення рівня КМОП

4. KL-34004 Експерименти зі схемами тригера, послідовної логіки та

лічильника

(1) Схеми тригерів

a. Побудова RS-тригера на базових логічних елементах

b. Побудова D-тригера на RS-тригерах

. Побудова схеми шумозаглушення на RS-тригерах

d. Побудова JK-тригера на D-тригерах

e. Поріг спрацьовування та затримка JK-тригера

f. Побудова синхронного двоступеневого JK-тригера на подвійних RS-

тригерах

g. Побудова реєстрації зсуву на D-тригерах

h. Реєстрація зсуву ліворуч/праворуч із попереднім встановленням

(2) Лічильники на JK-тригерах

a. Асинхронний двочний лічильник

b. Асинхронний двочний зворотний лічильник

c. Асинхронний десятичний лічильник

d. Синхронний потрійний лічильник

. Синхронний двочний лічильник

f. Синхронний двочний прямий/зворотний лічильник

g. Лічильник33

h. Кільцевий лічильник

5. KL-34005 Експеримент із генератором, імпульсним і навантаженням

прямим/зворотним лічильниками

(1) Побудова оперативного запам'ятного пристрою (ОЗП) на D-тригерах

(2) Схема 64-розрядного оперативного запам'ятного пристрої (ОЗП)

(3) Схема програмованого постійного запам'ятного пристрою

(СППЗП)

(4) Асинхронний чотирирозрядний двочний лічильник (на мікросхемі 7493)

(5) Двочний прямий/зворотний лічильник із попереднім встановленням

(6) Десятичний прямий/зворотний лічильник із попереднім встановленням

(7) Побудова схеми без повторного запуску на спеціалізованій мікросхемі

КМОН

(8) Побудова схеми з повторним запуском на мікросхемі КМОП

(9) Побудова схеми генератора імпульсів змінної скваності на подвійних

мультивібраторів, що чекають

6. KL-34006 Експеримент зі схемами пам'яті, світлодіодними матрицями,

ЦАП/АЦП та інтерфейс мікропроцесорного контролера

(1) Схема електронного СПЗП (ЕСППЗП)

(2) Експерименти зі схемою однополярного перетворення DAC0800

(3) Схема перетворення з біполярним виходом

(4) Експеримент з аналогом-цифровим перетворювачем ADC0804 8-розрядним

SAC

(5) Побудова лічильника динамічної розгортки на однокристальному

мікропроцесорі

7. KL-34007 Експеримент із цифровим і аналоговим таймерами, схемою

імпульсного генератора

(1) Побудова схеми генератора на базових логічних ейоментах

a. Резисторно-місткісний мультивібратор

b. Резисторно-місткісний кварцовий мультивібратор

(2) Побудова схеми генератора на логічному елементі Шмітта

a. Резисторно-місткісний генератор

b. Резисторно-місткісний генератор зі змінною сквагою

(3) Схема генератора на мікросхемі 555

a. Схема генератора 555

b. Схема генератора, керованої напругою

(4) Схеми мультивібраторів

a. Схеми низькошвидкісних мультивібраторів

b. Схема моновібратора з увімкненою/вимикною затримкою

c. Схема моновібратора, що чекає, з увімкненим/вимкненим таймером

d. Побудова схеми мультивібратора на мікросхемі 555

(5) Генератор сигналу з числовим керуванням

(6) Генератор із функцією точної частоти

(7) Генератор сигналу з числовим керуванням змінної скваності

(8) Експерименти з керуванням із різними увімкненими/вимкненими

затримками та перепади

(9) Точний 15-розрядний симетричний/асимометричний генератор ШІМ

8. KL-34008 Експеримент з безперервним порівнянням/SAC та АЦП з

двостадійним інтегрованням

(1) Експерименти з простим цифро-аналоговим перетворювачем з

однополярним виходом R-2R

(2) Експеримент із 8-розрядним аналогом-цифровим перетворювачем із цифровим

фронтом

(3) Експеримент із 8-розрядним аналогом-цифровим перетворювачем з

послідовною апроксимацією

(4) Експеримент із 8-розрядним аналогом-цифровим перетворювачем з

двостадійним інтегрованням

9. KL-34009 Клавіатура та дисплей для позиційного керування кроковим

двигуном

(1) Експеримент із контролем положення/ швидкості крокового двигуна

10. KL-34010 Точний цифровий таймер синхронізації

(1) Експеримент із синхронізацією

(2) Експеримент із таймером

11. KL-34011 Експеримент з універсальним пристроєм CPLD і монтажний

платою

(1) Створення блок-схеми/схематичної діаграми в Quartus II

(2) 16-розрядний 16-чний лічильник

(3) 16-розрядний десятичний лічильник

(4) 16-розрядний десятичний прямий/зворотний лічильник із попередньою

встановленням

(5) 16-розрядний контролер розгортання для 7-сегментного дисплея

(6) 16-розрядний прямий/зворотний лічильник і його індикація на 7-сегментному

дисплеї

(7) Електронна музична скринька

(8) Світлофор з анімацією й індикацією часу

- Ціна: Ціну уточнюйте